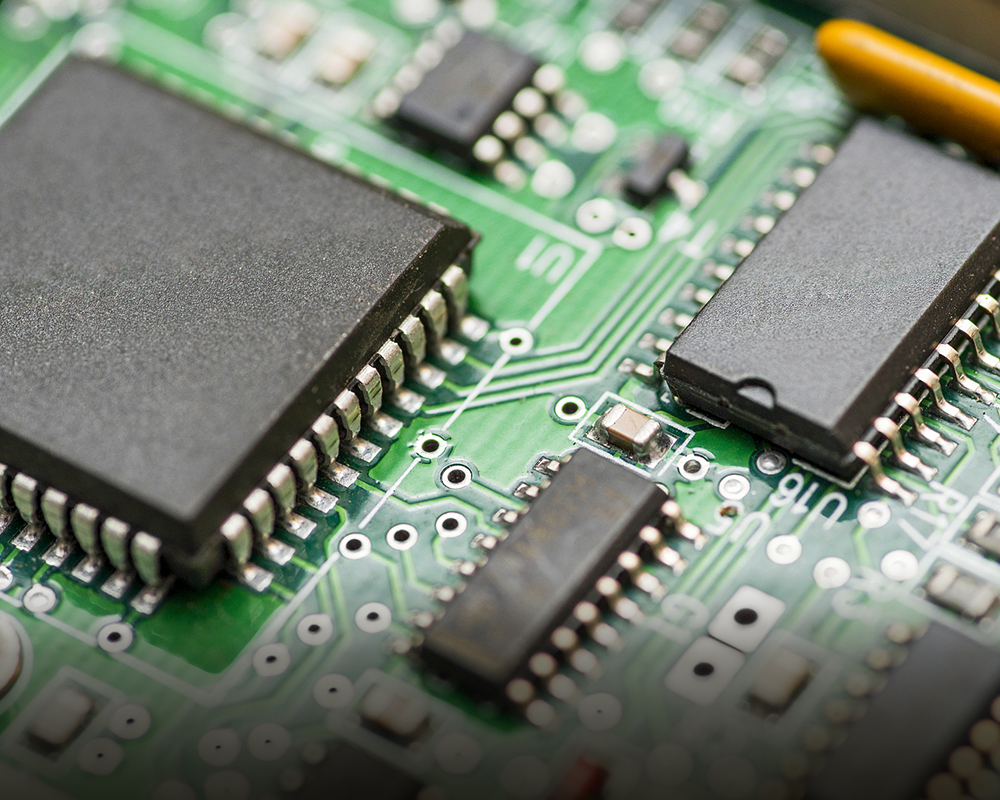

该芯片为车载 MCU 芯片,芯片适合车身电子、车身安全以及通用传感器节点等方面的应用。芯片内核基于 32 位 ARM Cortex-M3的内核,主频为 104MHz。内存控制器、DMA 控制器通过 AHB 总线与内核相连接。内核通过 32 位 AHB 总线与 24KB SRAM、256KB FLASH、以及 DMA 控制器相连接。I2C、MSCAN 等 接口模块以及 PIT 等定时器模块通过 APB 总线相连接,APB 总线外围设备通过 AHB-APB 总线桥与内核进行交互。该MCU 上电启动流程如下:在 MCU 系统启动时,首先会初始化内核时钟 并关闭看门狗。在初始化结束后,从地址 0x00000000 开始执行指令,建立中断向量表并初始化寄存器。然后 bootloader 将存储于 FLASH 的指令数据移动到 SRAM 中,MCU 在 SRAM 中执行取指操作。该系统的架构图如图1所示:

图1 车载MCU系统架构图

下面对该MCU挂载的各外设模块进行介绍:

(1)MCU时钟产生单元

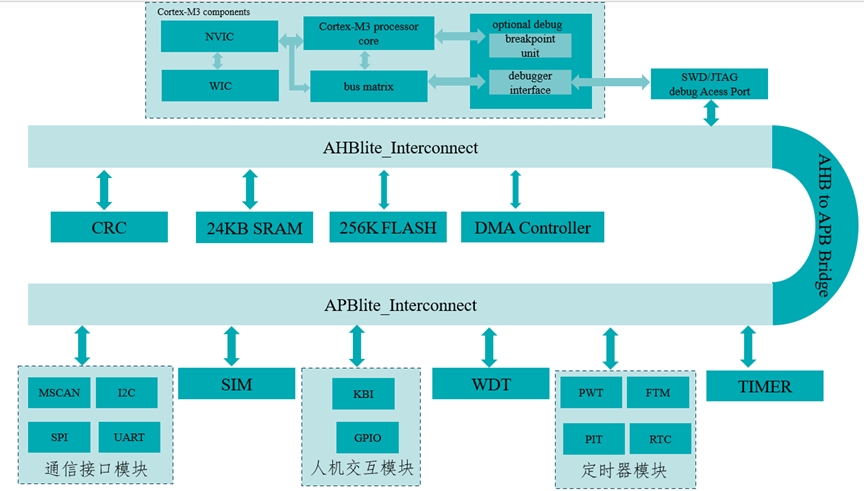

时钟产生单元(TIMER)为MCU提供多种时钟源选择,如锁频环时钟、内部或外部基准时钟。它还能产生震荡时钟供其他模块使用,并可作为自身的基准时钟源。通过编程选定时钟源和分频输出,可获得较低时钟频率。此外,时钟产生单元含电源管理模块,包括电压调节器、上电复位和低电压监测系统,用于在电压变动时保护存储器内容和控制MCU状态.TIMER的时钟结构图如图2所示。

图2 MCU 时钟产生单元结构图

(2)系统安全性模块

系统安全性模块包含看门狗(WDOG)和循环冗余校验(CRC)模块。

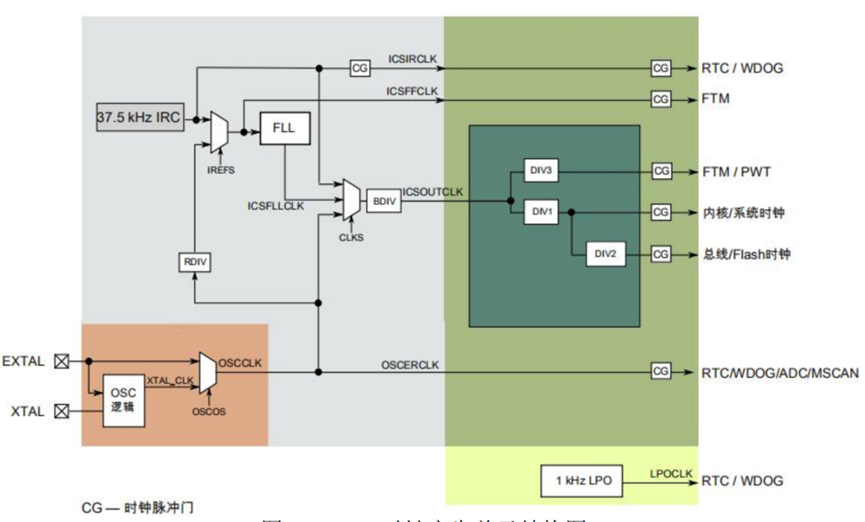

WDOG模块是独立定时器,监控软件执行并防止无限循环或指令错误,故障时复位MCU到已知状态。其计时溢出周期、窗口模式和时钟源可配置,但需在中断后128个时钟周期内完成。看门狗定时器的模块结构图如图3所示。

CRC模块用于生成数据传输的校验码。需编程特定参数、反演CRC结果、使能ASE位并编程初始值。每次设置新初始值或重新使用旧值时,都需重新初始化CRC模块以重新计算CRC值。所有参数设置需在初始值和数据值编程前完成。

图3 WDOG 模块结构图

(3)定时器模块

定时器模块包括FTM、PWT、PIT和RTC。

FTM是六通道计时器,支持捕获输入和比较输出,用于PWM信号生成和电机控制。其时钟源可配置,支持中心对齐PWM模式,通道可独立或成对输出,支持死区插入和双重边沿捕捉。

PWT是16位自由运行计数器,用于测量脉冲持续时间或信号边缘间时间。它可选择时钟源和分频,自动测量脉冲宽度,支持正、负脉冲测量,可配置触发沿和输入通道,生成脉宽测量完成和溢出中断。

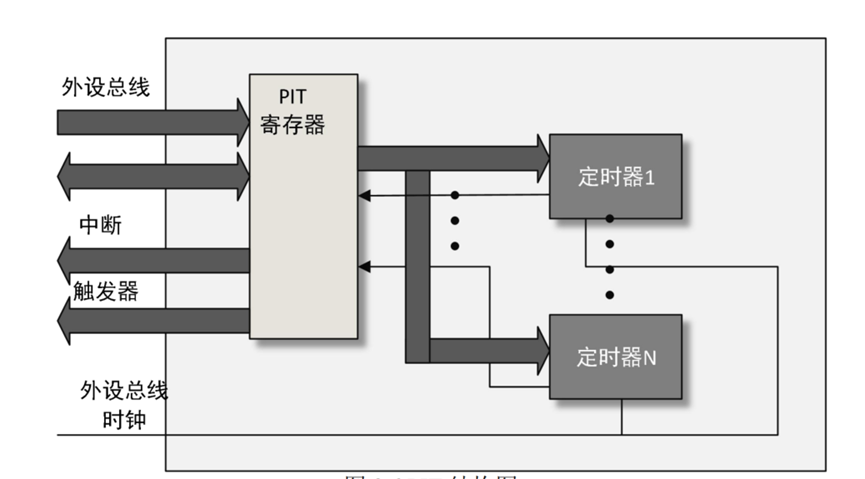

PIT是用于发起中断和触发的定时器总称,可选择输出通道用作ADC硬件触发,具有独立超时周期和屏蔽中断功能。

RTC是32位自由运行计数器,包含时钟源、比较器、可编程周期中断和预分频器,用于时间、日历任务调度。它允许设置比较值,当计数值与模数值相等时复位并生成中断,支持实时中断输出和锁存模数值。

图4 PIT结构图

(4)通信接口模块

通信接口模块包括SPI、I2C、MSCAN和UART。

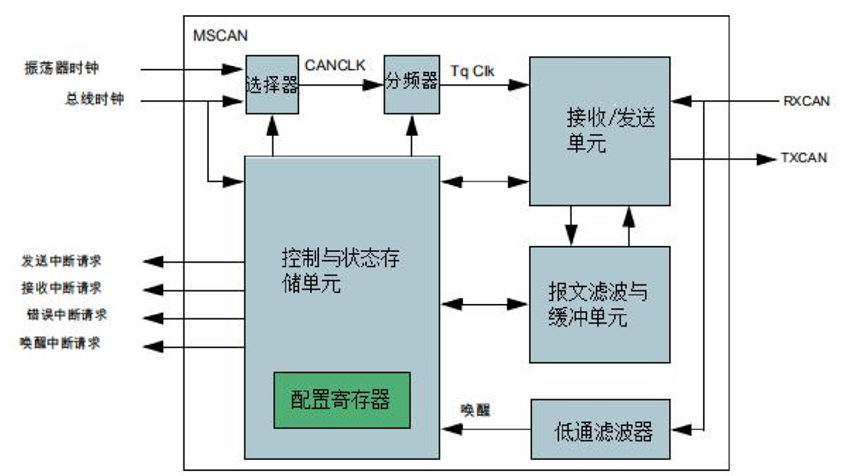

MSCAN是CAN通信控制器,用于汽车局域网互连,支持远程帧、FIFO存储、多种标识符滤波器和可编程唤醒功能,具有回环和监听模式,可标识错误状态,内部定时器用于时间标志,有三种工作模式。该MSCAN的模块结构图如图5所示。

SPI提供MCU和外设间的同步全双工串行通信,支持主机和从机模式,可配置传输比特率、时钟相位和极性,具有模式错误标志和选择性的移位优先级。

I2C用于器件间通信,支持100KB/s、400KB/s、3.4MB/s三种速度,最高波特率为时钟频率的二十分之一,具有SMBus特性。

UART允许MCU和远程设备间的全双工、异步、NRZ串行通信,要求相同的波特率,传输波特率允许偏差取决于同步和采样方式。

图5 MSCAN的模块结构图

(5)人机接口模块

人机接口模块含GPIO和KBI模块。

GPIO模块通过APB总线访问,零等待接口与内核通信,支持8/16/32位访问。配置数据方向寄存器控制数据方向,数据寄存器存储输出,输入数据寄存器显示引脚逻辑值。

KBI模块设计用于简化键盘矩阵连接,输入可作外部中断处理,唤醒MCU。最多8个引脚作额外中断源,通过控制寄存器使能或禁用中断,配置触发方式。

(6)直接内存访问控制器模块

直接内存访问模块控制器(DMA Controller)允许用户在不与 CPU 交互的前提下 将数据从存储器或外设寄存器移动到另一存储器地址空间或另一个外设寄存器中。 DMA 控制器和外设配置完成并处于活动状态时,会动态挂起外设的服务请求。DMA 禁用硬件服务请求存处于限制状态时,为了保持一致性,必须遵循特定的程序。DMA 控制器的数据移动分为内存到外设的数据移动、内存到内存的数据移动、外设到内存的数据移动和外设到外设的数据移动。