1.芯片功能及用途

在芯片功能方面,蓝牙音箱首先需要具备音频播放功能和蓝牙双模通信模块。 但市场上具备这两项功能的蓝牙芯片种类众多,为提升芯片的竞争力,本设计的蓝牙双模多媒体芯片还具备了插U盘播放音频功能、插SD卡播放音频功能及FM收音机等额外增值功能。但是这会使得芯片内部所要支持的功能众多,模块繁杂,数据难于处理。为解决该问题,在设计实现该芯片时将采用系统级芯片(SoC)的设计架构对芯片进行设计实现。

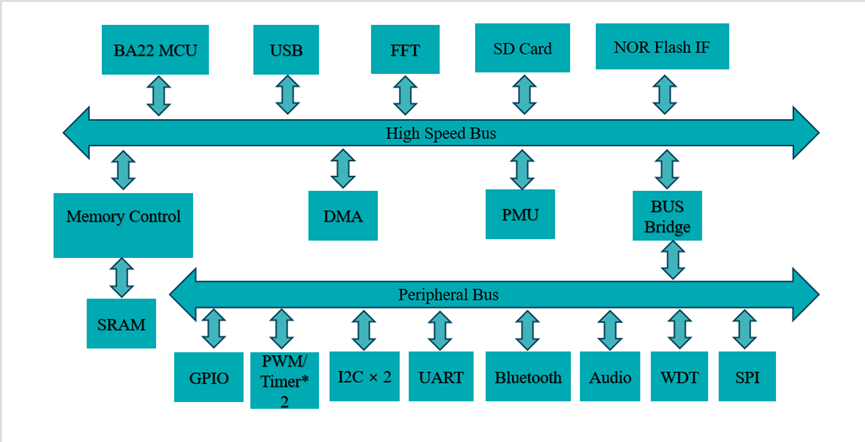

2.芯片架构及各部分

在设计本文中的系统级芯片时,设计工作包括对该系统中各功能模块的设计,这些功能模块包括:①主控制单元(MCU)②存储单元(Memory)③总线接口(Bus)④协处器(Co-processor)⑤外设功能模块(Peripherals)。蓝牙功能模块、U盘接口模块、SD卡接口模块及FM模块均为外设功能模块中的模块。芯片架构如图所示。

2.1主控制单元(MCU)

MCU在蓝牙芯片设计中,负责指令的执行、数据运算和系统调度。本文中的MCU设计基于IP集成方式,通过这一设计方式来控制蓝牙模块和多个外设接口。在MCU选型时,选择了32位架构,因为与16位和64位相比,32位更能满足便携式蓝牙音箱的寻址空间需求,同时符合低功耗、成本可控的设计目标。具体的MCU类型在设计中进行详细考察,除了MIPS32 M4K和ARM Cortex M4外,还参考了其他多家MCU型号,最终的选择综合考虑功耗、价格、 指令运行速度、占用面积、编译器指令复杂度及MCU所支持的功能等因素后选择BA22 MCU。

2.2存储单元(Memory)

存储单元分为高速易失性存储器和低速非易失性存储器两个部分。它们分别满足MCU数据交互的实时性需求和程序指令的长期保存需求。

高速易失性存储器:高速存储器采用RAM和ROM的组合,在此项目中由于蓝牙芯片设计是首次开发,程序需要多次修改和更新,因而ROM并不适用。RAM成为最佳选择,但由于其体积较大,占据芯片较多面积,因此在设计时需要仔细权衡RAM大小。通过FPGA平台的反复测试和验证,得出了最优的RAM存储空间,既保证了足够的程序存储能力,也实现了面积的优化。

低速非易失性存储器:低速非易失性存储器用于长期保存程序指令,常用的存储器包括一次性可编程存储器(OTP)、多次可编程存储器(MTP)、eFlash、NOR Flash和NAND Flash。在本项目中,设计必须支持多次反复擦写,OTP不适用。尽管MTP和eFlash可以支持多次编程,但它们在芯片内部实现成本较高:MTP在芯片内面积较大,而eFlash则需增加制造中的光照次数(增加15次),从而提升制造成本与周期。因此,这两种类型的存储器也被排除。

在外部存储器选择中,NAND Flash和NOR Flash有各自的适用场景。NAND Flash存储容量大于512MB,但功耗较高,适合大存储需求。而NOR Flash容量小于512MB,功耗较低,适合小存储需求。由于本项目成本要求较高,且存储需求相对较小,最终选择了成本和功耗较低的NOR Flash作为芯片的非易失性存储器。

2.3 总线接口(Bus)

在设计中,音频数据的传输需求并不高,因此选择低功耗、低面积的USB1.1 OTG协议足以满足性能要求。为实现USB接口,集成了Mentor公司的USB1.1 OTG IP。除此之外,还需要集成其他外设接口模块,例如SD卡接口(用于音乐播放)、I2C和SPI接口(用于连接显示屏)、UART接口(通用串口)及PWM/Timer模块(用于宽频调制和时间计算)。这些外设模块在以往项目中已有成熟设计,本次课题的重点是将其整合至SoC系统。

课题还选择使用AHB Lite总线接口,这是因为已有的音频模块、USB接口模块和SD接口模块在以往项目中均采用该总线接口,且与ARM系列MCU兼容性好。这种设计选择在MCU的具体型号选型时起到了重要参考作用。

2.4 协处理器(Co-processor)

尽管MCU已具备数据处理、计算和调度的能力,但在面对FFT运算、U盘及SD卡的大数据量音频播放等场景下,MCU的效率较低。因此,为提高处理能力,设计中加入了专用的音频FFT模块和DMA模块。这些模块用于加速FFT运算以及实现U盘和SD卡与音频模块之间的大数据搬运,从而有效提升了系统处理效率,减轻了MCU的负载。

2.5 外设功能模块(Peripherals)

根据蓝牙音箱的功能需求,芯片中需要实现多项外设功能模块,包括:

蓝牙双模模块:支持蓝牙4.1协议,具有标准蓝牙和低功耗蓝牙双模功能。标准蓝牙适用于大数据量的高速传输,而低功耗蓝牙则用于小数据量的传输。该模块硬件结构包括链路协议控制器(LPM)、基带调制解调器(Baseband)和模拟射频端(Radio Frequency),其中链路协议控制器主要依赖硬件实现。

音频模块:集成了的音频模块包含ADC、DAC和DTMF功能,用于数字-模拟信号转换及双音信号生成。该模块支持立体声播放,数据位宽为12位,采样率支持8KHz、16KHz、44.1KHz和48KHz,适应不同格式和音质的音频数据。

USB接口模块:根据需求,芯片集成了具备USB主功能的外设模块,用于支持U盘音乐播放。USB协议包括1.0、1.1、2.0和3.0版本,传输速率逐渐提升。出于面积与功耗考虑,选择USB1.1 OTG协议的12Mbps速率即可满足本设计10MB以内音频数据的传输需求。